在数字接口速度不断提高的背景下,信号完整性 (SI) 分析成为确保 IC-封装-PCB实现的必要条件。但同样重要的是要记住,电源完整性 (PI) 性能会影响高速接口的 SI。例如,电压降可以减少信号的眼图张开度和上升和下降时间,从而降低抖动裕度。因此,首先要检查的是PI是否满足产品目标,即电压纹波低于预定义值。完整的SIPI协同仿真是相关的,本次分享将借助SIwave开发的的先进流程,对单独封装PKG进行PDN网络Z11以及寄生参数的参数提取。

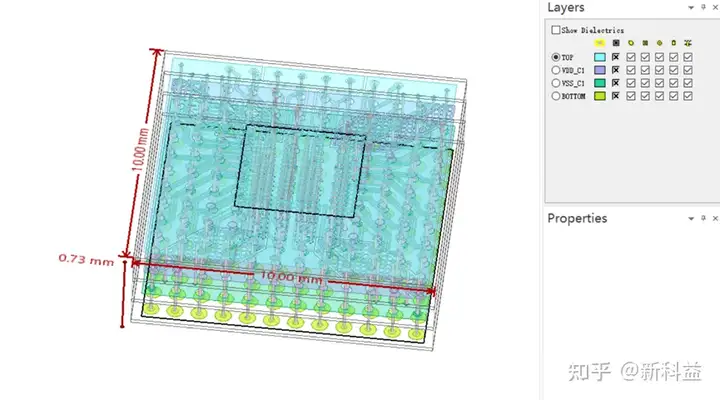

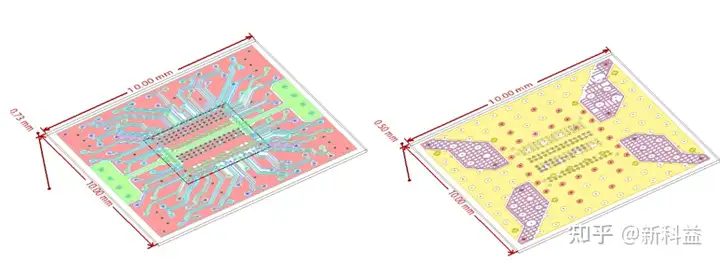

本次分析的PKG尺寸为10mm*10mm*0.73mm的四层板,具体如下:

第一层top层,第二层为电源层VDD,第三层为电源地层VCC,第四层为bottom层,详细叠层如下:

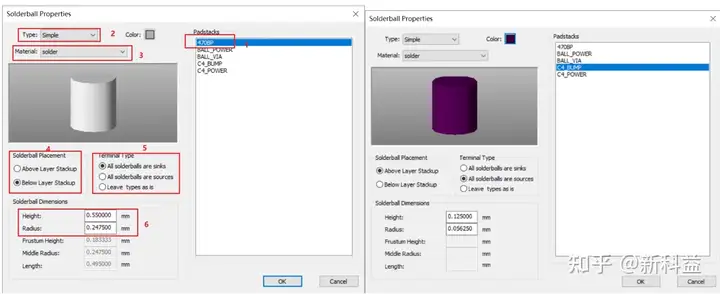

叠层设置与检查,此处不在浪费篇幅,大家可以参考上篇文章《ANSYS 针对BGA封装差分信号S参数的提取策略》,两者大同小异,为Package中焊球的设置(焊球类型、焊料材质以及用于RLGC参数提取的source和sink)

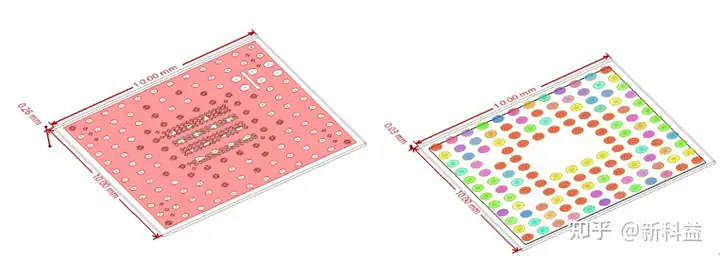

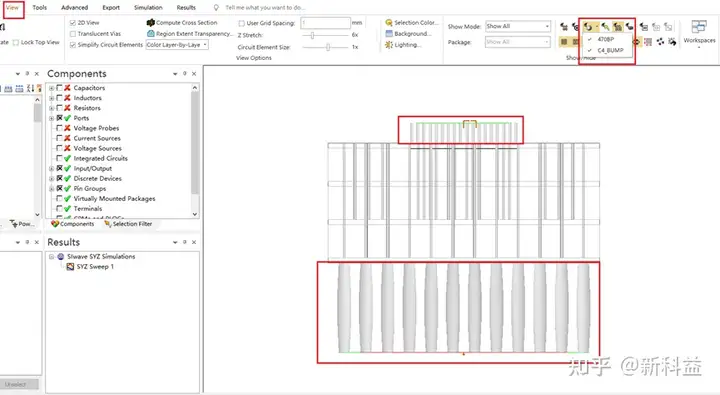

在“主页”选项卡中,选择“焊球属性”图标,打开“焊球属性”对话框。先选470B C4bump设置如下:。

其中470BP在为sink,C4 BUMP在上为source,同样焊球的显示与隐藏设置如下:

1.3选择电源网络,设置pin group和端口

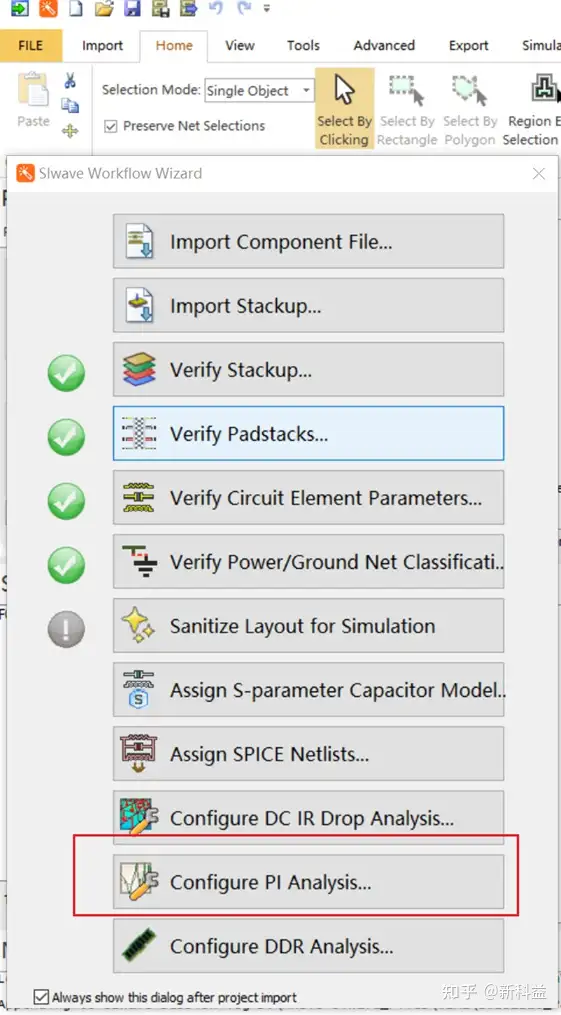

借助SIwave workflow进入PI流程

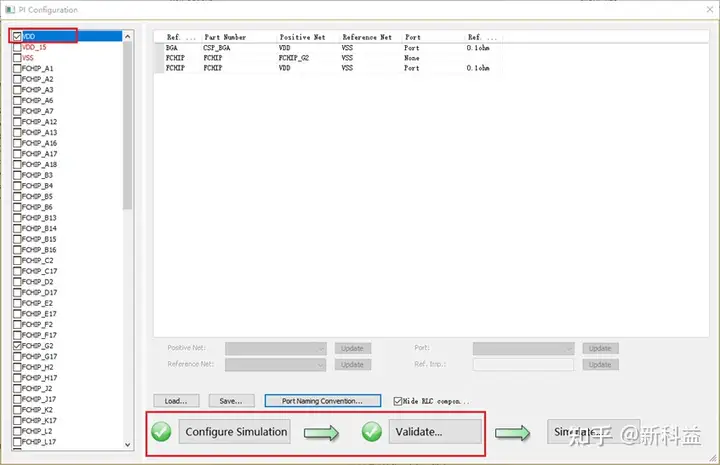

对要分析的电源的网络名称旁边打勾(选择 VDD),然后配置正负极以及阻抗(电源内阻0.1ohm),依次选择configure simulation和 validate..

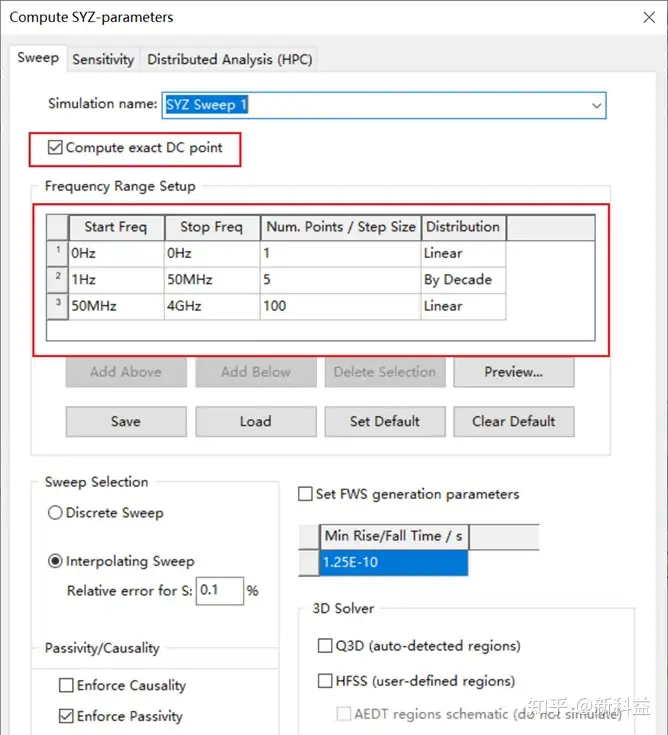

设置求解频率范围步长,然后开始求解。

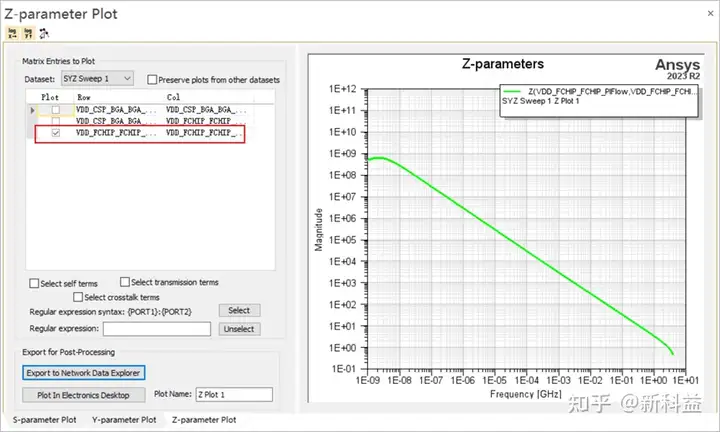

得到PDN阻抗Z11曲线如下:

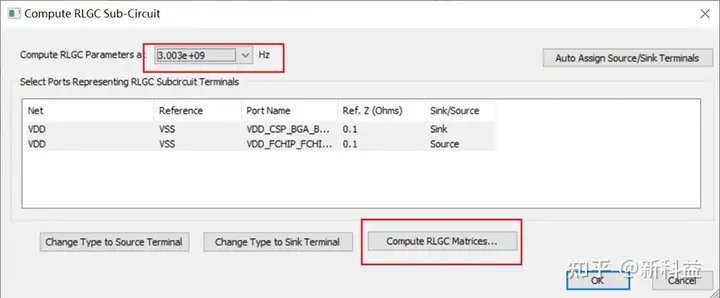

同样我们可以查看,任意频点的寄生参数,以3GHz为例的 PDN网络的RLCG参数提取如下:

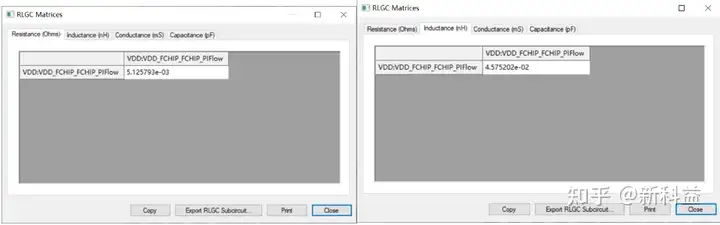

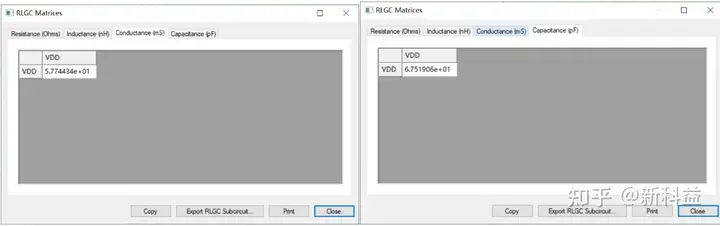

结果如下:

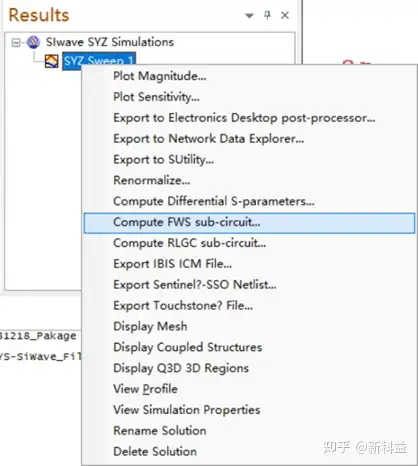

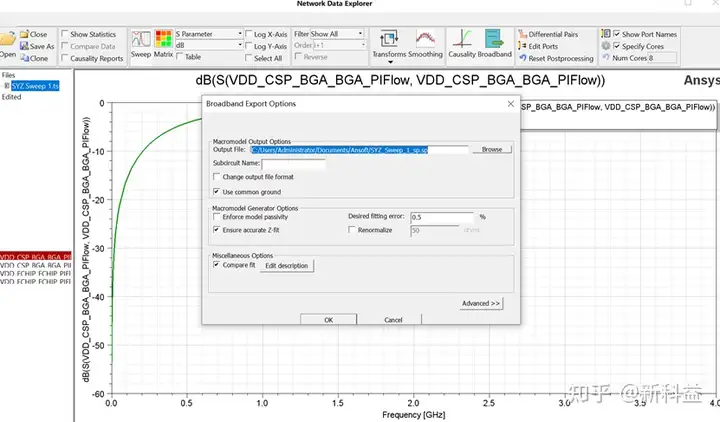

导出FWS(Full-Wave SPICE)模型参数,

本案例详细介绍了如何使用规范的SIwave PI分析流程对芯片封装PKG的PDN阻抗曲线进行研究,以方便查看整个电源网络的阻抗特性,然后提取封装的寄生参数,并导出全波子电路模型,为下一步的circuit瞬态有源分析做好准备。

|